# Impact of On-Chip Multi-Layered Inductor on Signal and Power Integrity of Underlying Power-Ground Net

<u>Akira Tsuchicya<sup>1</sup></u>, Akitaka Hiratsuka<sup>2</sup>,

Toshiyuki Inoue<sup>1</sup>, Keiji Kishine<sup>1</sup>, Hidetoshi Onodera<sup>2</sup> <sup>1</sup>The University of Shiga Prefecture <sup>2</sup>Kyoto University

This work is supported by JSPS KAKENHI (Grant Number 16K18092)

# Agenda

- Background and motivation

- Simulation setup

- Simulation results

- Conclusion and future work

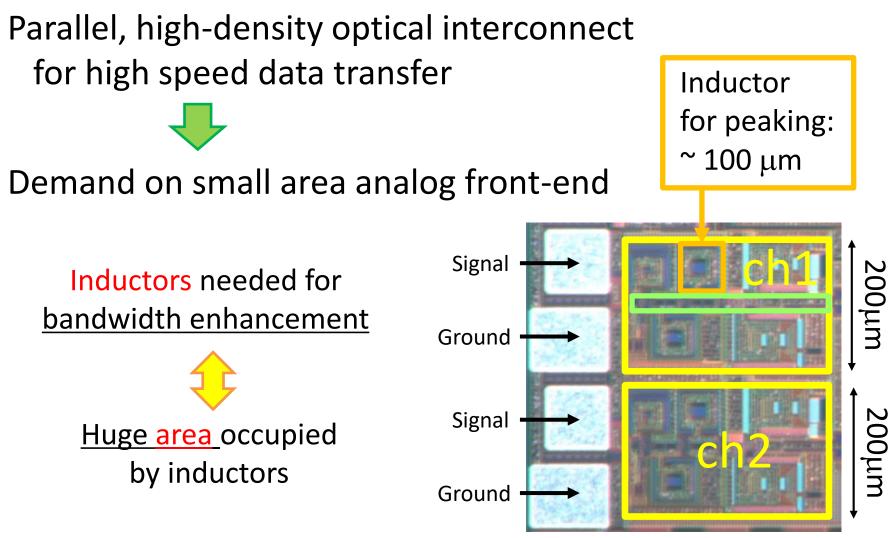

# Background

TIA + Post amp. 3

# **Small Area Inductor**

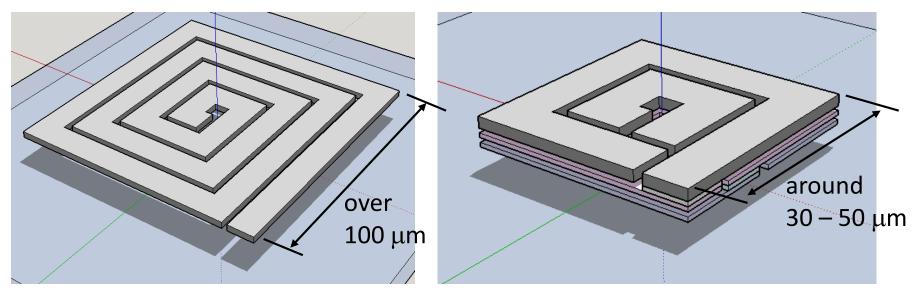

#### **Spiral Inductor**

#### **Solenoid Inductor**

✓ Top (Thick) metal only✓ High Q-factor

✓ Huge area

✓ Use lower layers

✓ Low Q-factor

✓ Small area

Solenoid inductor is effective for inductive peaking

### More Area-Saving

#### Is it OK to stack inductor on circuits?

Solenoid is smaller, but still needs >50µm□

#### Nothing under inductor

- ✓ Modeling accuracy

- ✓ Prevent coupling

If stacking is OK, we can save area more Aim of this paper: Investigating coupling between inductor and PDN

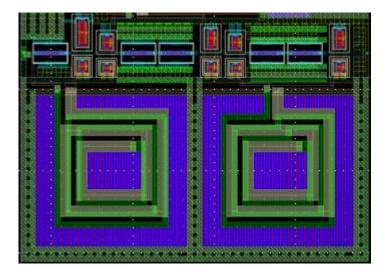

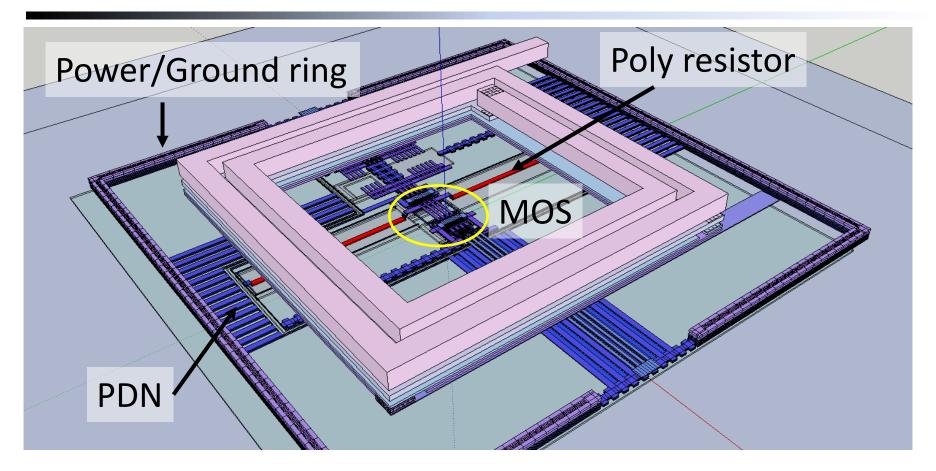

## **Stacking Inductor on Circuit**

Largest facing area to inductor is PDN (power delivery network) How should we design PDN under inductor?

# Agenda

- Background and motivation

- Simulation setup

- Power/Ground network structure

- Structure of inductor

- Simulation results

- Conclusion and future work

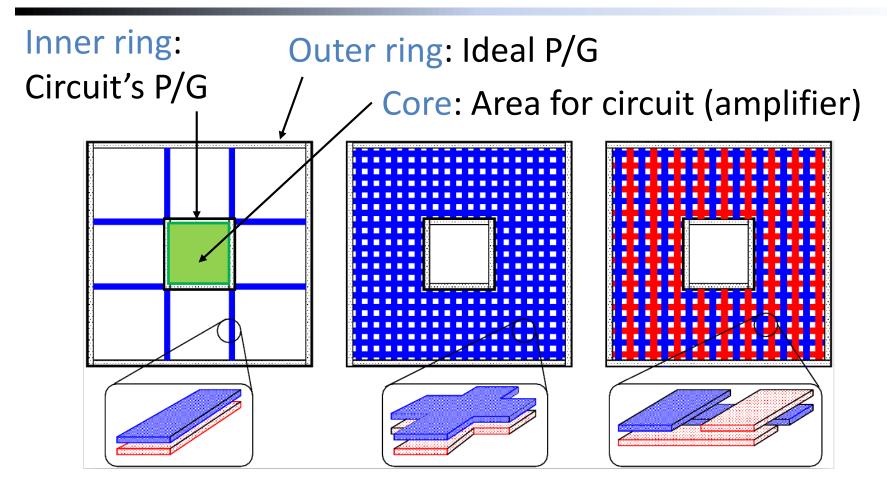

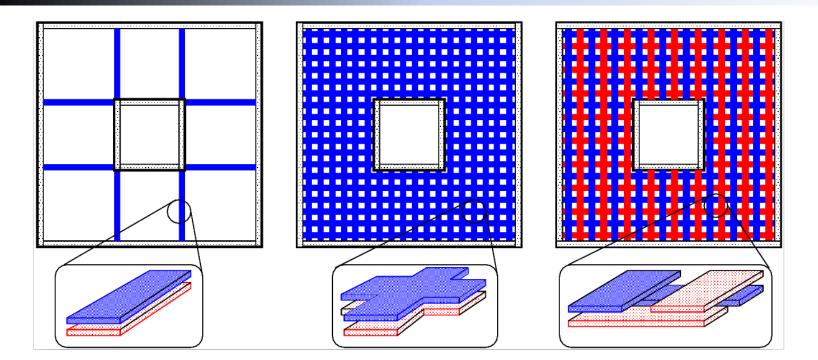

# **Power/Ground Structure**

(a) Sparse (b) Mesh (c) Woven

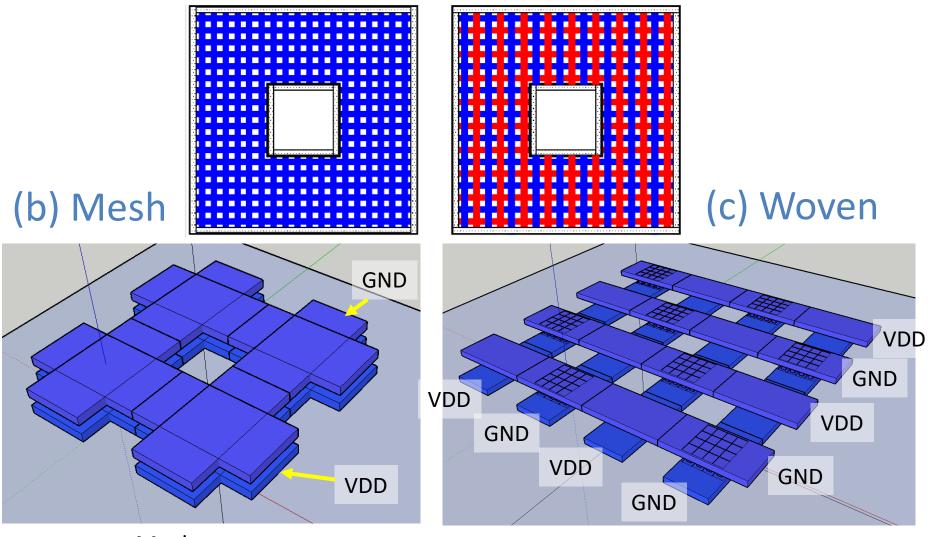

#### 3D Image of Mesh and Woven

Mesh structure

Woven structure

#### Comparison

(a) Sparse Minimize C coupling Small decoupling

#### (b) Mesh

M2 (GND) couples stronger Large decoupling

#### (c) Woven

Couplings are balanced Large decoupling

\* decoupling: decoupling capacitance between Vdd and GND 10

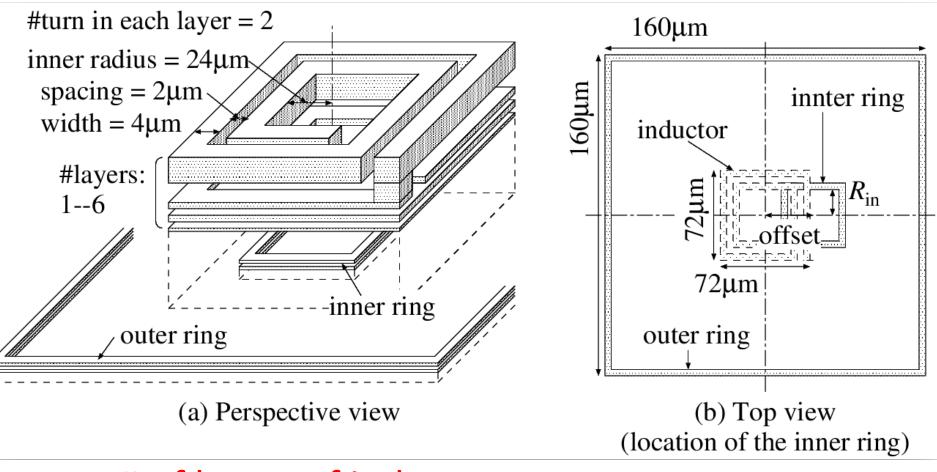

#### Parameters

#### # of layers of inductor Size and position of inner ring (core area)

# Agenda

- Background and motivation

- Simulation setup

- Simulation results

- Evaluation in inductance/capacitance value

- Evaluation in transient analysis

- Conclusion and future work

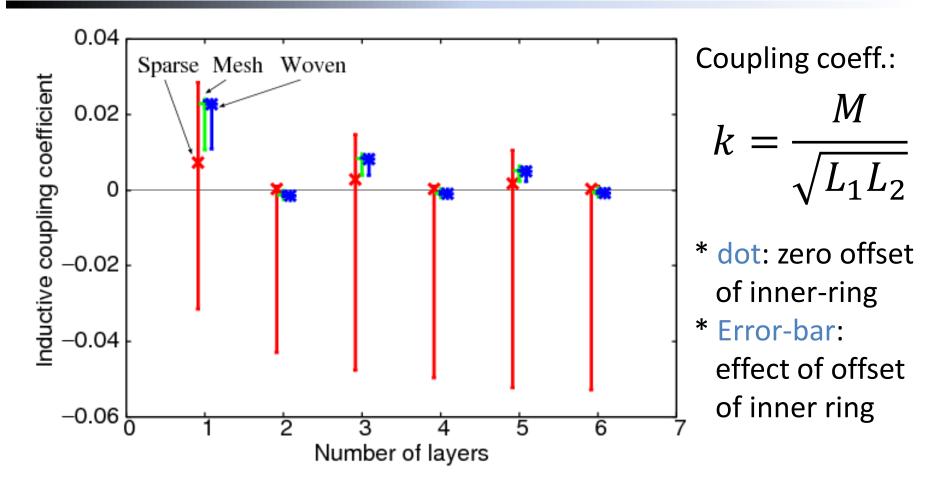

#### Inductive Coupling (Coupling Coeff.)

Increasing #layers = inductor get closer to PDN, but In Mesh and Woven, coupling coeff. decreases

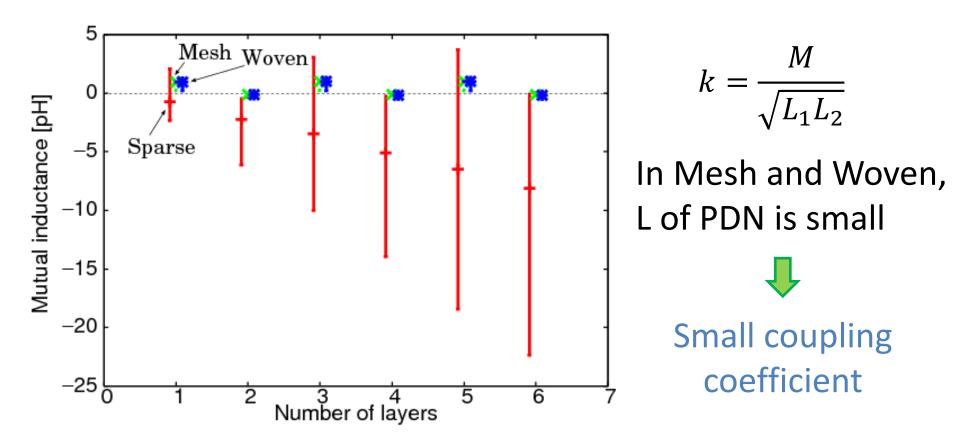

#### Inductive Coupling (Mutual Inductance)

Dense PDN can make inductive coupling almost zero even #layer increases

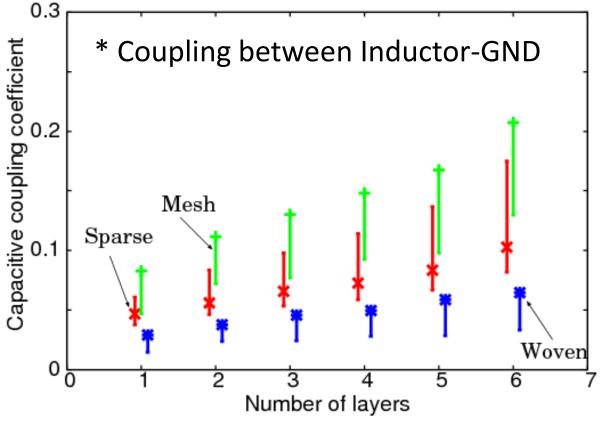

### Capacitive Coupling (Coupling Coeff.)

Much larger than inductive coupling coefficient (< 0.05)

#### Note:

Coupling of Mesh is largest, but Inductor-Vdd coupling of Mesh is almost zero

Sparse structure has larger coupling

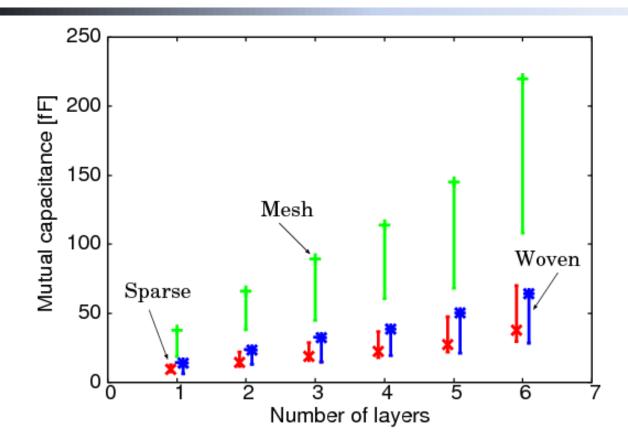

#### Capacitive Coupling (Coupling Capacitance)

Sparse is small or comparable to Woven, but Woven has larger Vdd-GND capacitance -> Coupling coefficient of Sparse becomes larger

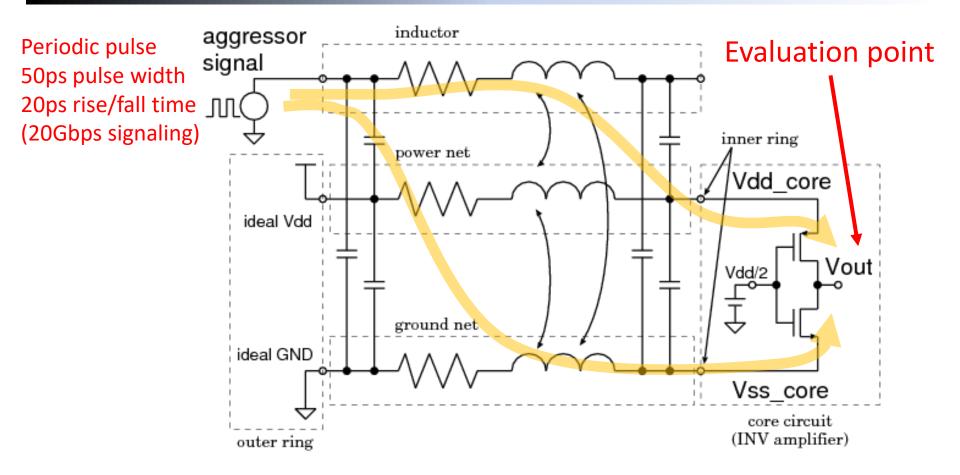

## **Transient Analysis on SPICE**

#### Coupled $\pi$ -model for power/ground/inductor network

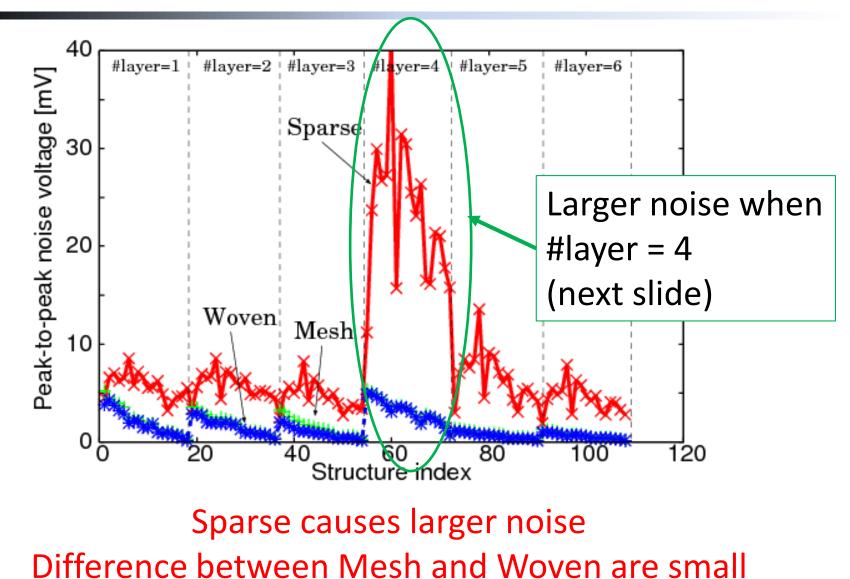

#### Noise Peak-to-peak Voltage

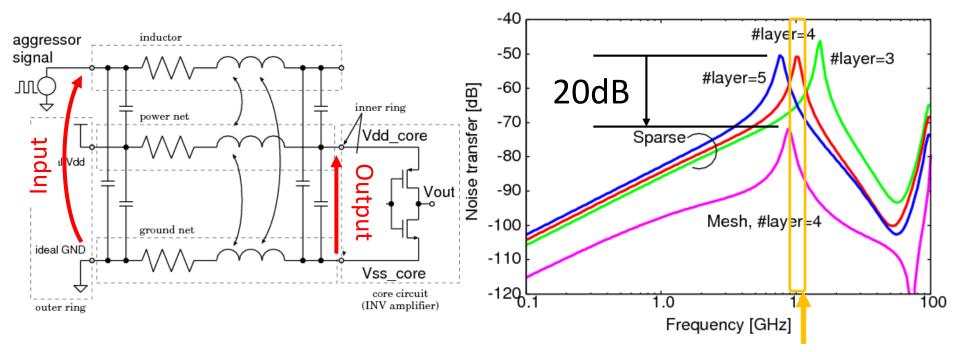

### Impact of Resonance

#### Noise transfer function from aggressor to inner ring

Aggressor input is 20Gbps = 10GHz clock

Mesh also has resonant frequency near 10 GHz, but transfer function is 20dB smaller

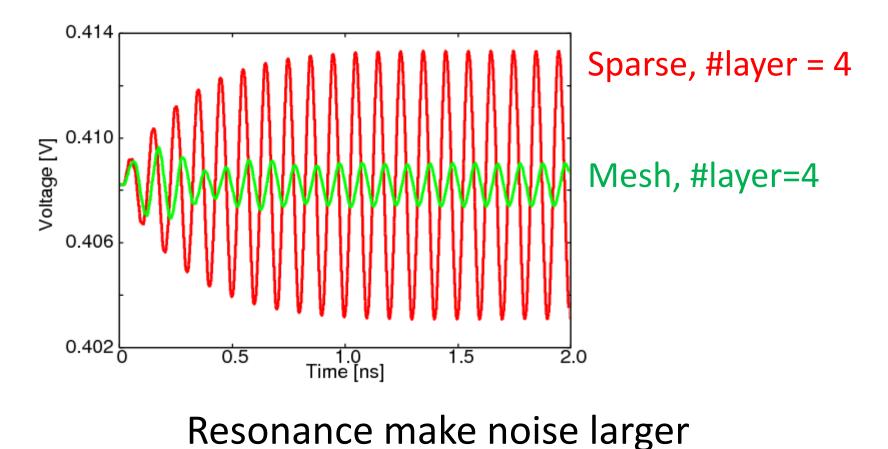

#### Noise Waveform

Mesh and Woven can reduce impact of resonance

# Agenda

- Background and motivation

- Simulation setup

- Simulation results

- Conclusion and future work

# Summary

Coupling of inductor and PDN is investigated

- Stacking Inductor on circuit

- Test 3 structures: Sparse, Mesh, Woven

- PDN should have dense P/G wires

- Even inductor get closer, Mesh and Woven are better than Sparse

- Sparse has a risk of large noise due to resonance

- Dense structure (Mesh and Woven) can suppress the impact of resonance

## Future Work

#### Remaining questions:

- Coupling to substrate is not discussed

- Mesh/Woven might shield coupling to substrate

- Is lumped model adequate?

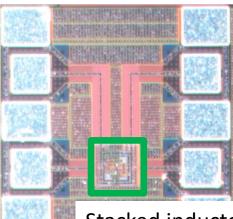

#### Chip fabrication is completed Now we are preparing real chip measurement

Stacked inductor/amp.